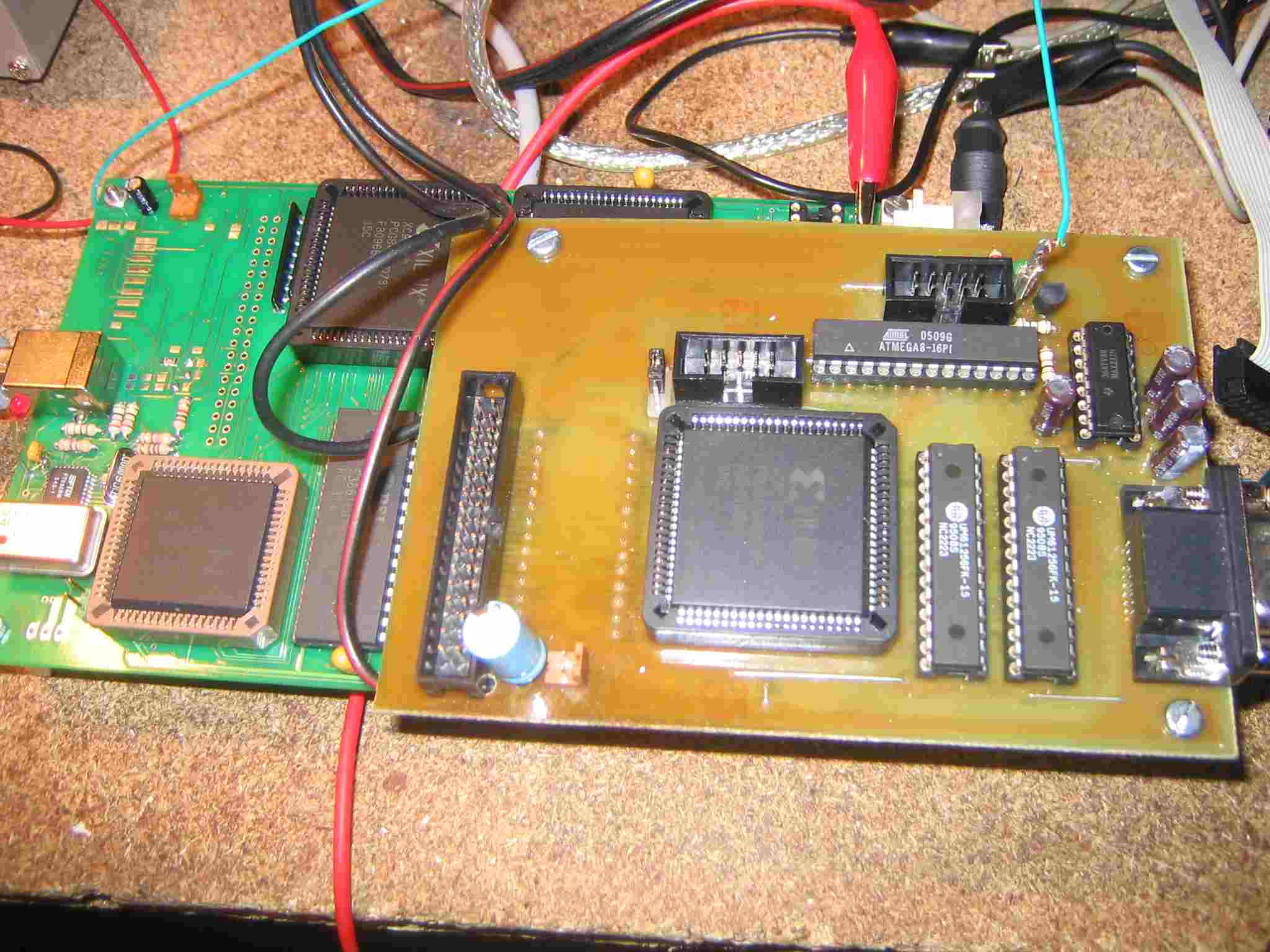

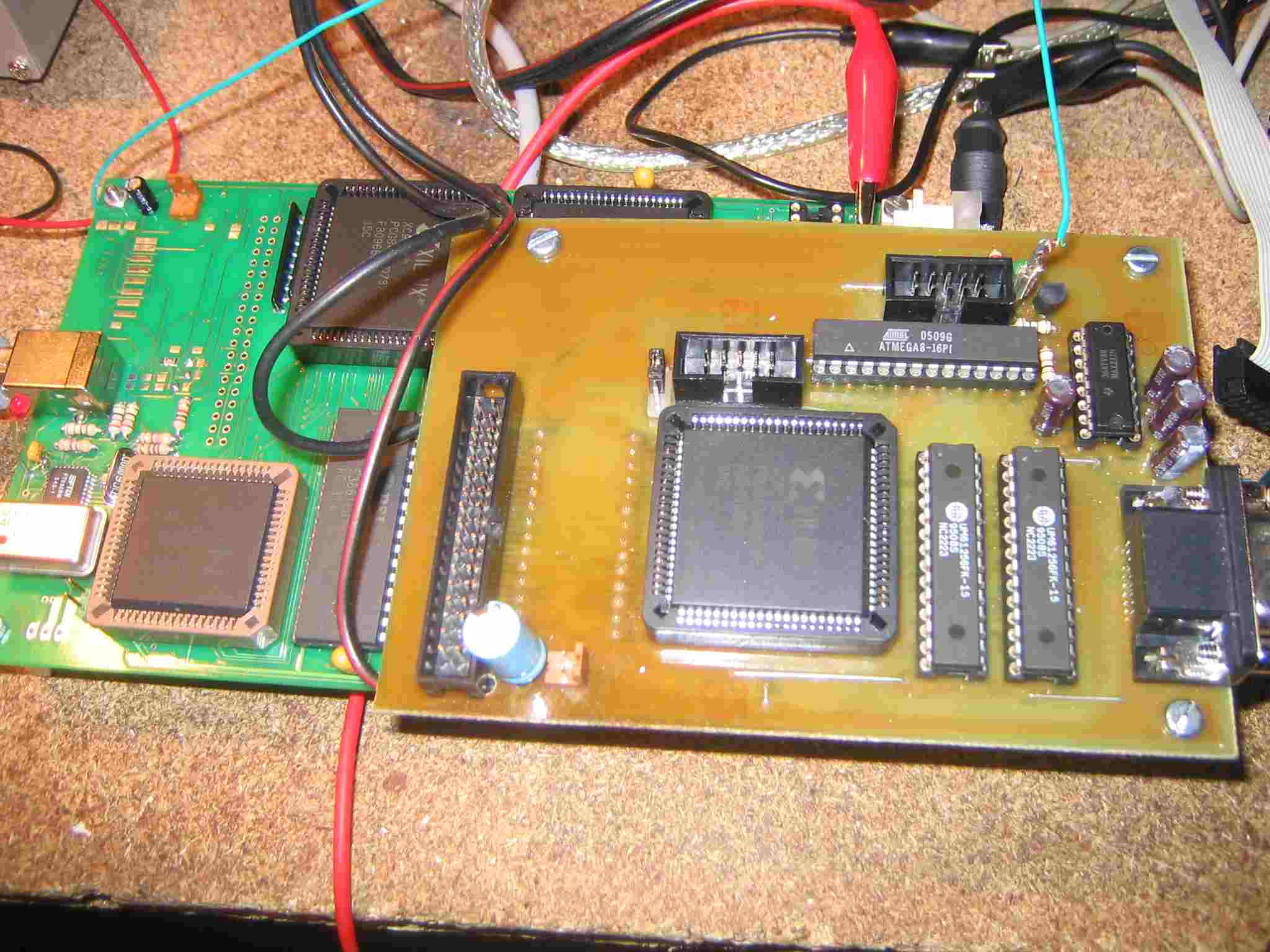

64K Eprom Simulator

I implemented this project for a Z180 board. It is based on Holger Klabundes Design. He

implemented a simulator based on a xilinx 9572 and a pic. Holgers

version is using a parallel port interface.

I have not yet used PIC's so i decided to implement a version with

an AVR mega 8, a Xilinx 9572 and a serial port interface. The software

for the AVR is written in GCC, the host software for Linux or Win32 is

written in FreePascal. The

code for the xilinx cpld is written in VHDL.

Until now i have only used the simulator with a 20 MHz Z180 systems

but it works fine. The loader software has the following features:

- works under Linux and Win32

- Baudrate 115200

- checksums for data transfer

- Binary or Intel Hex file support

- Verify command

- Memfill command

- Memcopy command

- Offset in ram can be specified

- Source under GPL

The current board uses the internal oscillator of the mega 8. Therefore

the oscillator has to be adjusted to 7,3 MHz. In eprsim.c, uncomment

the #define BOARDTEST, connect a terminal and use the O command to

determine the correct value for OSCCAL (i used 0x91). After you have

done that, compile the AVR code without the define BOARDTEST and use

the eprsim --comtest command to test communication.

I used two 32 KB cache RAMS from and old 486 board. The access time of

the RAMs is 15ns, the XPLD needs 20-25 ns so the access time should be

faster than an Eprom (thas fastst 27256 i have has 70ns). (See Datasheet for the UM61256)

What could be done better:

- using an XTAL instead of the internal oscillator

- remove XILINX and AVR programming ports to make the board smaller

- add a jumper to disconnect power from the eprom socket

The following downloadable file contains the XILINX VHDL Sources, the

gcc sources for the AVR, the FreePascal source for the host programm

and the eagle schematic and board file for the single sided board.

download

last change Jan 15, 2008 Armin. Impressum